# ATAES132A

# ATAES132A 32K AES Serial EEPROM Complete Data Sheet

# Features

- Crypto Element Device with Secure Hardware-Based Key Storage

- 32 kb Standard Serial EEPROM Memory

- Compatible with the Microchip AT24C32D and the Microchip AT25320B

- 16 User Zones of 2 kb Each

- High-Security Features

- AES Algorithm with 128-bit Keys

- AES-CCM for Authentication

- Message Authentication Code (MAC) Capability

- Guaranteed Unique Die Serial Number

- Secure Storage for up to Sixteen 128-bit Keys

- Encrypted User Memory Read and Write

- Internal High-Quality FIPS Random Number Generator (RNG)

- 16 High-Endurance Monotonic EEPROM Counters

- Flexible User Configured Security

- User Zone Access Rights Independently Configured

- Authentication Prior to Zone Access

- Read/Write, Encrypted, or Read-Only User Zone Options

- High-Speed Serial Interface Options

- 10 MHz SPI (Mode 0 and 3)

- 1 MHz Standard I<sup>2</sup>C Interface

- 2.5V to 5.5V Supply Voltage Range

- <250 nA Sleep Current

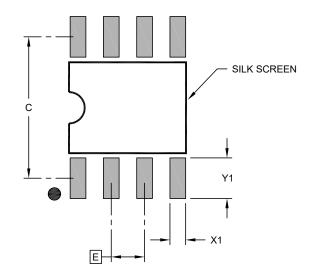

- 8-pad UDFN and 8-lead SOIC Package Options

- Temperature Range: -40°C to +85°C

# Applications

- Easily Add Security by Replacing Existing Serial EEPROM

- Authenticate Consumables, Components, and Network Access

- Protect Sensitive Firmware

- Securely Store Sensitive Data and Enable Paid-for Features

- Prevent Contract Manufacturers from Overbuilding

- Manage Warranty Claims

- Securely Store Identity Data (i.e. Fingerprints and Pictures)

# Description

The Microchip ATAES132A is a high-security, Serial Electrically-Erasable and Programmable Read-Only Memory (EEPROM) providing both authentication and confidential nonvolatile data storage capabilities. Access restrictions for the 16 user zones are independently configured, and any key can be used with any zone. In addition, keys can be used for standalone authentication. This flexibility permits the ATAES132A to be used in a wide range of applications.

The AES-128 cryptographic engine operates in AES-CCM mode to provide authentication, stored data encryption/decryption, and Message Authentication Codes. Data encryption/decryption can be performed for internally stored data or for small external data packets, depending upon the configuration. Data encrypted by one ATAES132A device can be decrypted by another, and vice versa.

The ATAES132A pinout is compatible with standard SPI and I<sup>2</sup>C Serial EEPROMs to allow placement on existing PC boards. The SPI and I<sup>2</sup>C instruction sets are identical to the Microchip Serial EEPROMs. The extended security functions are accessed by sending command packets to the ATAES132A using standard write instructions, and reading responses using standard read instructions. The ATAES132A secure Serial EEPROM architecture allows it to be inserted into existing applications.

The ATAES132A device incorporates multiple physical security mechanisms to prevent the release of the internally stored secrets. Secure personalization features are provided to facilitate third-party product manufacturing.

# **Pin Configuration and Pinouts**

| Pin             | Function                                                                               |

|-----------------|----------------------------------------------------------------------------------------|

| NC              | No Connect                                                                             |

| CS              | SPI Mode: Chip Select<br>I <sup>2</sup> C Mode: NC                                     |

| SO              | SPI Mode: Serial Data Out<br>I <sup>2</sup> C Mode: NC or Authorization Output (AUTHO) |

| SDA/SI          | SPI Mode: Serial Data In<br>I <sup>2</sup> C Mode: Serial Data I/O                     |

| SCK             | SPI Mode: SPI Clock Input<br>I <sup>2</sup> C Mode: SCL Clock Input                    |

| VCC             | Positive Supply Connection                                                             |

| V <sub>SS</sub> | Ground Supply Connection                                                               |

### Table 1. Pin Configuration

### Figure 1. Pinouts

| <b>8-Lead</b><br>(Top V                               |   | 1 | <b>8-Lead UDFN</b><br>(Top View)                  |                                        |

|-------------------------------------------------------|---|---|---------------------------------------------------|----------------------------------------|

| CS [] 1<br>SO [] 2<br>NC [] 3<br>V <sub>SS</sub> [] 4 | 8 |   | 1     8       2     7       3     6       4     5 | V <sub>CC</sub><br>NC<br>SCK<br>SI/SDA |

See Section 8. Pin Lists for pin list and description.

# **Table of Contents**

| Fea | atures       | 5                                          | 1  |

|-----|--------------|--------------------------------------------|----|

| Ар  | plicati      | ons                                        | 1  |

| De  | script       | ion                                        | 2  |

| Pin | Cont         | iguration and Pinouts                      | 2  |

| 1.  | Intro        | duction                                    | 7  |

|     | 1.1.         | Scope                                      | 7  |

|     | 1.2.         | Conventions                                |    |

|     | 1.3.<br>1.4. | Abbreviations                              |    |

| 2   |              | ory                                        |    |

| ۷.  |              | -                                          |    |

|     | 2.1.         | User Memory                                |    |

|     | 2.2.<br>2.3. | Key Memory                                 |    |

|     | 2.3.<br>2.4. | Configuration Memory<br>SRAM Memory        |    |

| 3.  | Secu         | rity Features                              | 16 |

|     | 3.1.         | Architecture                               |    |

|     | 3.2.         | Authentication                             |    |

|     | 3.3.         | Encrypted Memory Read/Write                |    |

|     | 3.4.         | Data Encryption/Decryption                 |    |

|     | 3.5.         | Keys                                       |    |

|     | 3.6.         | Random Numbers                             |    |

| 4.  | Secu         | rity Configuration Registers               | 19 |

|     | 4.1.         | User Zone Configuration                    | 19 |

|     | 4.2.         | Key Configuration                          | 20 |

|     | 4.3.         | VolatileKey Configuration                  |    |

|     | 4.4.         | Counter Configuration                      | 23 |

| 5.  | Stan         | dard Serial EEPROM Read and Write Commands | 24 |

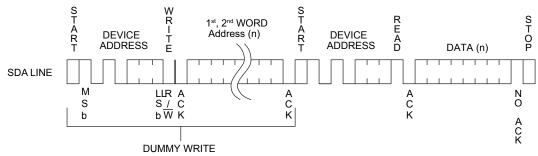

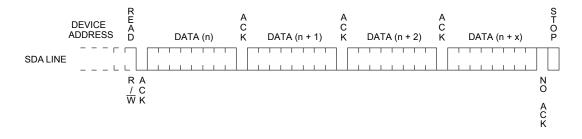

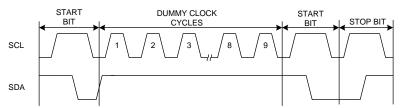

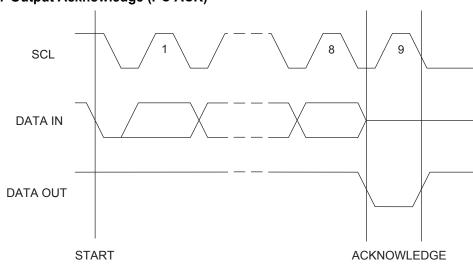

|     | 5.1.         | Read                                       | 24 |

|     | 5.2.         | Write                                      | 25 |

| 6.  | Com          | mands                                      | 27 |

|     | 6.1.         | Command Block and Packet                   |    |

|     | 6.2.         | Command Summary                            |    |

|     | 6.3.         | ReturnCode                                 | 30 |

| 7.  | Com          | mand Definitions                           | 32 |

|     | 7.1.         | Auth Command                               |    |

|     | 7.2.         | AuthCheck Command                                    | 34   |

|-----|--------------|------------------------------------------------------|------|

|     | 7.3.         | AuthCompute Command                                  | . 35 |

|     | 7.4.         | BlockRead Command                                    | . 36 |

|     | 7.5.         | Counter Command                                      | 37   |

|     | 7.6.         | Crunch Command                                       | . 38 |

|     | 7.7.         | DecRead Command                                      | 39   |

|     | 7.8.         | Decrypt Command                                      | 40   |

|     | 7.9.         | EncRead Command                                      | 42   |

|     | 7.10.        | Encrypt Command                                      | 44   |

|     | 7.11.        | EncWrite Command                                     | 45   |

|     | 7.12.        | INFO Command                                         | 47   |

|     | 7.13.        | KeyCreate Command                                    | . 48 |

|     | 7.14.        | KeyImport Command                                    | . 50 |

|     | 7.15.        | KeyLoad Command                                      | 51   |

|     | 7.16.        | KeyTransfer Command                                  | . 52 |

|     | 7.17.        | Legacy Command                                       | . 53 |

|     | 7.18.        | Lock Command                                         | 54   |

|     | 7.19.        | Nonce Command                                        | 56   |

|     | 7.20.        | NonceCompute Command                                 | 57   |

|     | 7.21.        | Random Command                                       | . 59 |

|     | 7.22.        | Reset Command                                        | 60   |

|     | 7.23.        | Sleep Command                                        | 61   |

|     | 7.24.        | WriteCompute Command                                 | 62   |

| 8   | Pin I        | ists                                                 | 64   |

| 0.  |              |                                                      |      |

|     | 8.1.<br>8.2. | Package Pin List (SOIC and UDFN)<br>Pin Descriptions |      |

|     | 0.2.         |                                                      | . 04 |

| 9.  | Elect        | rical Characteristics                                | 65   |

|     | 9.1.         | Absolute Maximum Ratings                             | 65   |

|     | 9.2.         | Reliability                                          | 65   |

|     | 9.3.         | DC Characteristics                                   |      |

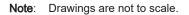

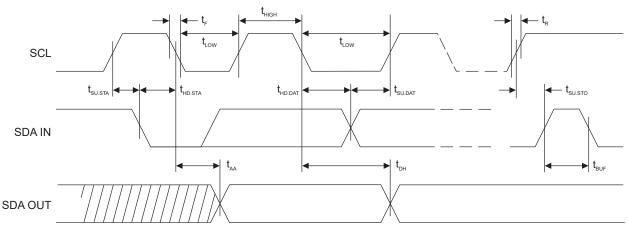

|     | 9.4.         | AC Characteristics                                   | 67   |

| 10. | Appe         | endix A. Standards and Reference Documents           | .70  |

| 11. | Appe         | ndix B. Memory Map                                   | 71   |

| 12. | Арре         | endix C. User Memory Map                             | 73   |

| 13. | Арре         | endix D. Command Memory Map                          | 74   |

| 14. | Арре         | endix E. Configuration Memory Map                    | .77  |

| 15. | Арре         | endix F. Key Memory Map                              | .88  |

| 16. | Арре         | endix G. Understanding the STATUS Register           | 90   |

| 17. Appendix H. Understanding Counters1               | 104 |

|-------------------------------------------------------|-----|

| 18. Appendix I. Cryptographic Computations1           | 107 |

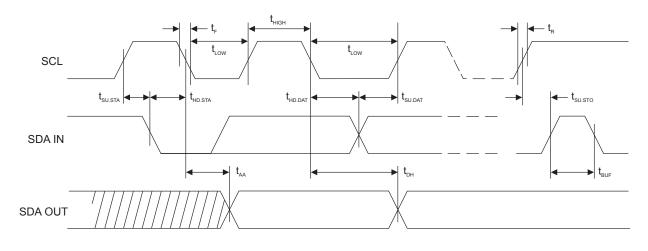

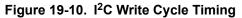

| 19. Appendix J. I <sup>2</sup> C Interface1           | 123 |

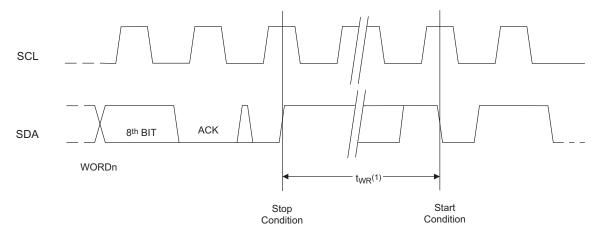

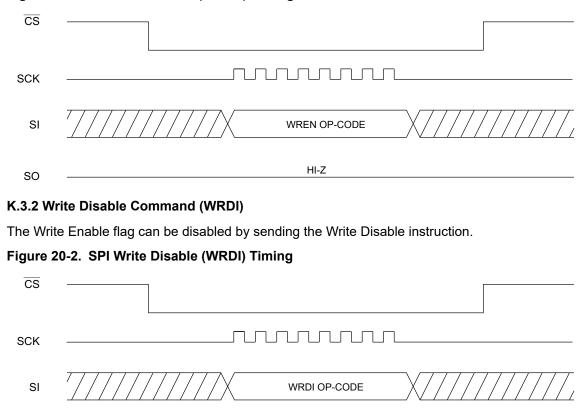

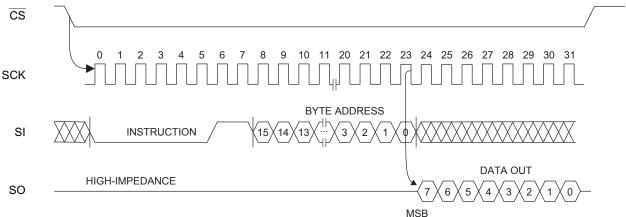

| 20. Appendix K. SPI Interface 1                       | 132 |

| 21. Appendix L. Power Management 1                    | 139 |

| 22. Appendix M. Block Checksum1                       | 146 |

| 23. Appendix N. ATAES132A Command Response Time1      | 147 |

| 24. Appendix O. Default Configuration1                | 151 |

| 25. Appendix P. Serial Memory Backward Compatibility1 | 154 |

| 26. Errata1                                           | 159 |

| 27. Package Marking Information1                      | 160 |

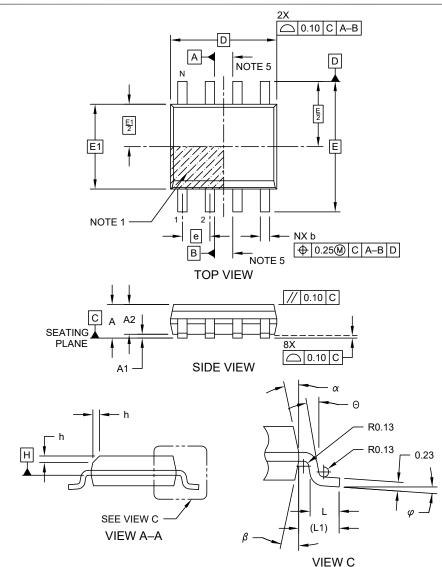

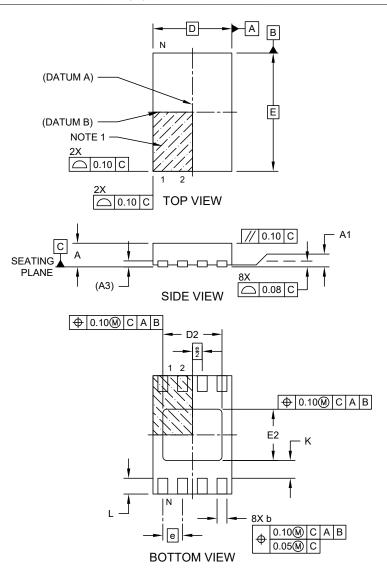

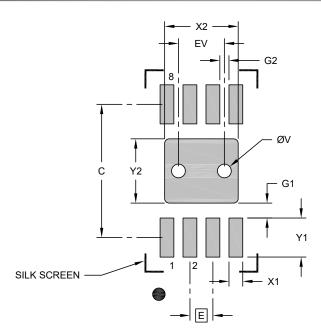

| <ul><li>28. Package Drawings</li></ul>                | 161 |

| 29. Revision History1                                 | 167 |

| The Microchip Web Site 1                              | 168 |

| Customer Change Notification Service1                 | 168 |

| Customer Support 1                                    | 168 |

| Product Identification System1                        | 169 |

| Microchip Devices Code Protection Feature1            | 170 |

| Legal Notice1                                         | 170 |

| Trademarks 1                                          | 170 |

| Quality Management System Certified by DNV1           | 171 |

| Worldwide Sales and Service1                          | 172 |

# 1. Introduction

The ATAES132A provides 32 kb of EEPROM user data memory, sixteen 128-bit Key Registers, sixteen high-endurance monotonic EEPROM Counters, factory unique Die Identification Numbers, and a Configuration Memory. The Configuration Memory registers control access to the User Memory, as well as the restrictions on Key and Counter functionality.

The User Memory can be accessed directly with standard SPI or I<sup>2</sup>C commands if a user zone is configured for open or read-only access. If the user zone security is activated, then the extended ATAES132A command set is used to access the contents of a user zone. The extended ATAES132A commands are executed by writing the command packet to the virtual memory using standard SPI or I<sup>2</sup>C Write commands. The response packet is retrieved by reading it from the virtual memory using standard SPI or I<sup>2</sup>C Read commands.

The ATAES132A packages are compatible with standard SPI and I<sup>2</sup>C EEPROM footprints. This allows the ATAES132A to be inserted into many existing Serial EEPROM applications.

# 1.1 Scope

This Specification provides all specifications for configuration and operation of the ATAES132A .

# 1.2 Conventions

### Table 1-1. Nomenclatures

| Nomenclature           | Definition                                                             | Notes                                                                                   |

|------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Host                   | The SPI or I <sup>2</sup> C Master<br>Device                           | The Host initiates all communications with slave devices on the serial interface bus.   |

| Client                 | The ATAES132A Secure<br>Serial EEPROM Defined by<br>this Specification | Operates as a SPI or I <sup>2</sup> C slave.                                            |

| nnb                    | Binary Number                                                          | Denotes a binary number "nn" (most-significant bit on the left).                        |

| 0xZZZZ                 | Hexadecimal Number                                                     | Denotes hex number ZZZZ (most-significant bit on the left).                             |

| zzzz <sub>h</sub>      | Hexadecimal Number                                                     | Denotes hex number ZZZZ (most-significant bit on the left).                             |

| RegName.FieldName      | Field Name                                                             | Reference to bit field FieldName in register RegName.                                   |

| RegArray[xx].FieldName | Field Name                                                             | Reference to bit field FieldName in register RegArray[xx], where xx is the array index. |

| ByteVal <x:y></x:y>    | Bit Field                                                              | Reference to specific bits in a register or command parameter byte.                     |

| UZ                     | User Zone                                                              | Reference to a User Zone number.                                                        |

| CntID                  | Counter ID                                                             | Reference to a Counter number.                                                          |

| KeyID                  | Key ID                                                                 | Reference to a Key Register number.                                                     |

### 1.2.1 Byte Order

The ATAES132A device uses a big-endian coding scheme and utilizes the same bit and byte orders as a standard Serial EEPROM. The byte order is identical to the NIST AES specifications (see Appendix A. Standards and Reference Documents):

- The most significant bit of each byte is transmitted first on the bus.

- The most significant byte of multi-byte integers is transmitted prior to the least significant byte. This applies to the CRC, address, and other 16-bit command parameters.

- All arrays are transmitted in index order, with byte index 0 first.

- Configuration fields that are more than eight bits appear on the bus during a Read or Write in the index order in which they appear in this specification. The top byte in the input parameters table is byte<0> and appears first on the bus. These fields are arrays of bytes, not multi-byte integers.

### 1.3 Abbreviations

#### Table 1-2. Abbreviations

| Abbreviation | Phrase                          | Definition                                                                                         |

|--------------|---------------------------------|----------------------------------------------------------------------------------------------------|

| AES          | Advanced Encryption<br>Standard | Block cipher algorithm standardized by NIST with 128-bit block size.                               |

| AES-CCM      | AES Cipher Chaining<br>Message  | AES mode using the Counter with Cipher Block Chaining-Message Authentication Code Algorithm.       |

| AES-ECB      | AES Electronic Code Book        | AES mode using the Electronic Code Book Algorithm.                                                 |

| Ciphertext   |                                 | Data communicated after it has been encrypted.                                                     |

| Cleartext    |                                 | Data communicated in a nonencrypted state.                                                         |

| MAC          | Message Authentication<br>Code  | A 128-bit value used to validate the authenticity of ciphertext.                                   |

| Nonce        | Number Used Once                | A value used in cryptographic operations.                                                          |

| Plaintext    |                                 | Data which is either the input to an encryption operation or the output of a decryption operation. |

| RFU          | Reserved For Future Use         | Any feature, memory location, or bit that is held as reserved for future use by Microchip.         |

| RNG          | Random Number Generator         | Produces high-quality random numbers.                                                              |

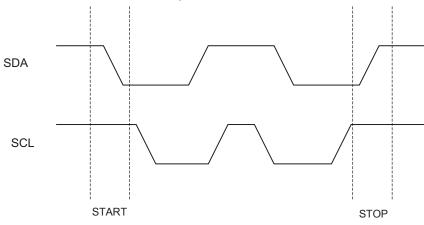

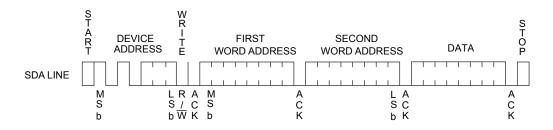

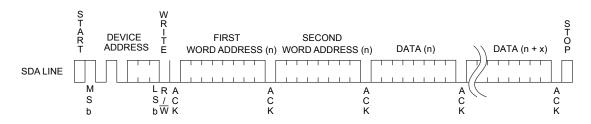

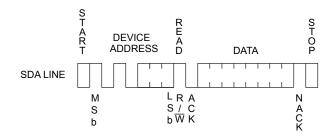

# 1.4 Communication

The ATAES132A is designed to interface directly with SPI and I<sup>2</sup>C microcontrollers. The read and write commands are similar to the standard Microchip Serial EEPROM commands for ease of use. Since the ATAES132A pinout is also similar to standard Serial EEPROMs, it is possible to use the ATAES132A on existing PC boards in some cases.

When Read and/or Write access to a user zone is unrestricted, the memory is accessed using the standard I<sup>2</sup>C or SPI Read and Write commands. Similarly, if Authentication Only is required and the authentication requirement has been satisfied, then the memory is accessed directly by the Host using standard I<sup>2</sup>C or SPI Read and Write commands.

If the Host begins a Read operation in an open user zone but continues reading until a prohibited section of memory is reached, the ATAES132A will continue to increment the address and will return 0xFF for each byte in the restricted user zone. If the Host begins a Read operation in an open user zone but continues reading beyond the end of the User Memory, the ATAES132A will return 0xFF for each byte requested, but will stop incrementing the address.

All other operations, including the execution of the extended commands, are performed by using the standard I<sup>2</sup>C or SPI Read and Write commands to exchange data packets via the command and response memory buffers. The Device Status Register reports the state of the device and is used for handshaking between the Host and the ATAES132A.

### 1.4.1 Sending ATAES132A Commands

The ATAES132A commands described in Section 7. Command Definitions, are executed by writing the command block to virtual memory (Appendix D. Command Memory Map) using standard SPI or I<sup>2</sup>C Write commands. The response block is retrieved by reading it from virtual memory using standard SPI or I<sup>2</sup>C Read commands.

### 1.4.1.1 Command Memory Buffer

The Command Memory Buffer is a write-only memory buffer that is used by writing a command block to the buffer at the base address of  $0 \times FE00$ . After the Host completes its Write operation to the buffer, the ATAES132A verifies the integrity of the block by checking the 16-bit checksum, and then executes the requested operation. See Section Command Block and Packet for a description of the command packet. See Appendix D. Command Memory Map for additional Command Memory Buffer information.

#### Table 1-3. Command Memory Buffer Map

| Base Address | Base<br>+ 1 | Base<br>+ 2 | Base<br>+ 3 |        |        | <br>      | Base<br>+ N-2 | Base<br>+ N-1 |

|--------------|-------------|-------------|-------------|--------|--------|-----------|---------------|---------------|

| Count        | Opcode      | Mode        | Param1      | Param1 | Param2 | <br>DataX | CRC1          | CRC2          |

### 1.4.1.2 Response Memory Buffer

The Response Memory Buffer is a read-only memory buffer that is used by reading a response from the buffer at the base address of  $0 \times FE00$ . The base address of the Response Memory Buffer contains the first byte of the response packet after an ATAES132A command is processed. See Section Command Block and Packet for a description of the response packet. See Appendix D.2 Response Memory Buffer for additional Response Memory Buffer information.

### Table 1-4. Response Memory Buffer Map Following a Crypto Command

| Base Address | Base<br>+ 1 | Base<br>+ 2 | Base<br>+ 3 |       | <br> |       | Base<br>+ N-2 | Base<br>+ N-1 |

|--------------|-------------|-------------|-------------|-------|------|-------|---------------|---------------|

| Count        | ReturnCode  | Data1       | Data2       | Data3 | <br> | DataX | CRC1          | CRC2          |

The Response Memory Buffer is also used to report errors which occur during execution of standard  $I^2C$  or SPI Write commands. When the  $I^2C$  or SPI command execution is complete (as indicated by the STATUS Register), the Response Memory Buffer contains a block containing an error code (ReturnCode) if an error occurred, otherwise it contains a block with ReturnCode =  $0 \times 00$ . See Section ReturnCode, for the error descriptions.

### 1.4.2 Device Status Register (STATUS)

The Device Status Register is used for handshaking between the Host microcontroller and the ATAES132A . The Host microcontroller is expected to read the STATUS Register before sending a command or reading a response.

The read-only Device Status Register at address  $0 \times FFF0$  reports the current status of the ATAES132A device. This register can be read with the standard I<sup>2</sup>C or SPI Read Memory commands. The SPI Read Status Register command can also be used to read the STATUS Register, as described in Appendix K. Read Status Register Command (RDSR).

Reading the STATUS Register does not increment the Memory Read Address, and so a Host microcontroller can easily monitor the ATAES132A device status by repeatedly reading the STATUS Register. See Appendix G. Understanding the STATUS Register for a detailed description of the STATUS Register bits and Status Bit behavior.

#### Table 1-5. Device Status Register Definition

| Bit 7 | Bit 6 | Bit 5    | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|----------|-------|----------|-------|-------|-------|

| EERR  | RRDY  | Reserved | CRCE  | Reserved | WAKEb | WEN   | WIP   |

The Device Status Register can always be read when the ATAES132A is configured for SPI interface mode, even if the ATAES132A is processing a command or writing the EEPROM. When the ATAES132A is configured for I<sup>2</sup>C interface mode, the Host can read the STATUS Register only when the I<sup>2</sup>C Device Address is ACKed.

If the ATAES132A is in the Sleep or Standby power state, reading the STATUS Register forces the ATAES132A to wake up; the STATUS Register is 0xFF until the wake-up process is complete.

# 2. Memory

The ATAES132A EEPROM is a nonvolatile memory which is divided into several sections with each section having a different function. The User Memory section contains 32 kb for data storage. The Configuration Memory section contains the configuration information, security control registers, and counters. The Key Memory stores the 16 secret keys used to perform cryptographic functions. The EEPROM page length is 32 bytes. The ATAES132A SRAM buffers and registers are located near the top of the memory address space and are accessed using standard EEPROM Read/Write commands.

The complete memory map is shown in Appendix B. Memory Map. Each portion of the memory is described briefly in the following sections.

# 2.1 User Memory

The 32 kb User Memory is organized as 16 user zones of 2 kb each. Each user zone has an associated user zone configuration register in the Configuration Memory. A user zone can only be accessed when the security requirements specified in the associated user zone configuration register have been satisfied. All bytes within a user zone have the same access restrictions. Since the user zone access restrictions are independently configured, the security requirements for each user zone can be unique. Any key can be used with any user zone.

Each user zone can be configured to require authentication, Read Encryption, Write Encryption, a combination of these, or no security. The User Memory can be accessed directly with standard SPI or I<sup>2</sup>C commands if a user zone is configured for open or read-only access. If the user zone security is activated, then the extended ATAES132A command set is used to access the contents of a user zone.

### 2.1.1 Automatic Post Write Data Verification

The Write and EncWrite commands include an automatic data verification function. After the EEPROM Write is complete, the Data Verification Logic reads the new EEPROM contents and compares it to the data received from the Host. If the data does not match, the ATAES132A sets the EERR bit in the STATUS Register and returns a DataMatch error code. If the data is correct, then the ReturnCode indicates success.

# 2.2 Key Memory

The Key Memory securely stores 16 keys which are each 128 bits long. Each key has an associated Key Configuration Register in the Configuration Memory. Keys can only be used for the cryptographic functions enabled in the Key Configuration Register. Individual keys can be configured to require a successful authentication prior to use. Key values can never be read from the ATAES132A under any circumstances. See Appendix F. Key Memory Map.

The Key Memory can be written prior to locking with either encrypted or cleartext data. Encrypted writes are performed using the EncWrite command (see Section EncWrite Command). Cleartext writes are performed using the standard SPI or I<sup>2</sup>C Write commands (see Section Write). After locking, the Key Registers are managed with the KeyCreate, KeyImport, KeyLoad, and KeyTransfer commands. The KeyTransfer command allows the User Memory to be used as the Extended Key Memory; eight keys can be stored in each user zone (see Section KeyTransfer Command).

# 2.3 Configuration Memory

The Configuration Memory contains all of the registers which control user zone access requirements, the Key usage restrictions, and the Counter usage restrictions. Device-level Configuration Option Registers are also located in Configuration Memory.

The ATAES132A Configuration Memory includes a register programmed with unique, read-only die identification data at the factory. The Configuration Memory also contains several registers for customer information. The Configuration Memory registers can always be read using the BlockRead command (see Section BlockRead Command). The Lock command is used to permanently lock the contents of the Configuration Memory after personalization (see Section Lock Command).

See Table 2-1 for a summary of the Configuration Memory registers sorted by register name. See Appendix E for the Configuration Memory Map.

### 2.3.1 Counters

The ATAES132A includes 16 high-endurance EEPROM Counters. Each Counter has or can:

- An associated Counter Configuration Register in the Configuration Memory,

- Only be incremented,

- Never be decremented or reset,

- Be used to track system usage or to store small values.

A key can be configured to prevent exhaustive attacks by limiting key usage with a Counter.

Each counter can increment up to a value of 2,097,134 using the Count Command, after which they can be no longer changed. Counters attached to keys are incremented each time the key is used; when the Usage Counter reaches its limit, the key is disabled. The Counters include a power interruption protection feature to prevent corruption of the Count value if power is removed during the increment operation.

On shipment from Microchip, the EEPROM locations are initialized to their lowest value. The initial value of each Counter may be written to a different value prior to personalization and prior to locking the configuration. See Appendix H. Understanding Counters.

# 2.4 SRAM Memory

The ATAES132A SRAM is used to store volatile data and status information. The ATAES132A SRAM buffers and registers are mapped into the top of the memory address space and are accessed using the Standard EEPROM Read/Write commands.

- The Command Memory Buffer is used to send extended commands to the device.

- The Response Memory Buffer is used to read responses to the extended commands from the device.

- An IO Address Reset Register is used to reset the buffer address pointers.

- The STATUS Register reports the state of the device.

- The VolatileKey register and the Authentication Status Register are stored in the SRAM and are managed by the internal logic. These registers cannot be directly written or read by the user.

#### 2.4.1 Nonce

The SRAM is used to store the Nonce and Random Number Generator (RNG) Seed. The RNG Seed is generated automatically by ATAES132A, as described in Section Random Numbers. The Nonce is

generated using the Nonce command or the NonceCompute command. The Nonce and RNG Seed Register are erased when the device loses power, enters the Sleep state, or is reset.

### 2.4.2 VolatileKey

The SRAM contains a session key register named VolatileKey. This key location can be written with the KeyCreate, KeyImport, KeyLoad, or KeyTransfer commands. The VolatileKey register is erased when the device loses power, enters the Sleep state, or is reset. Restrictions on VolatileKey are established when the register is created or loaded and persist until the power is lost or the key is reloaded.

VolatileKey can never be used to read or write the User Memory or to increment the Counters. VolatileKey can only be used to perform authentication operations and to encrypt or decrypt external data. See Section VolatileKey Configuration for the VolatileKey usage restrictions.

#### 2.4.3 Command Memory Buffer

The Host executes extended ATAES132A commands by writing a command block to the Command Memory Buffer using a standard SPI or I<sup>2</sup>C Write command. After the Host completes its write operation to the SRAM buffer, ATAES132A verifies the integrity of the block by checking the 16-bit Checksum and then executes the requested operation.

#### 2.4.4 Response Memory Buffer

The Host receives responses to the extended ATAES132A commands by reading a response block from the Response Memory Buffer using a standard SPI or I<sup>2</sup>C Read command. The base address of the Response Memory Buffer contains the first byte of the response packet after an ATAES132A command is processed.

### 2.4.5 IO Address Reset Register

Writing the IO Address Reset Register causes the address pointers in the Command Memory Buffer and the Response Memory Buffer to be reset to the base address of the buffers. Writing the IO Address Reset Register does not alter the contents of the Response Memory Buffer or the value of the STATUS Register.

#### 2.4.6 Device Status Register (STATUS)

The Device Status Register is used for handshaking between the Host microcontroller and ATAES132A . The Host is expected to read the STATUS Register before sending a command or reading a response. Reading the STATUS Register does not alter the contents of the Command Memory Buffer, the Response Memory Buffer, or the value of the STATUS Register. See Appendix G. Understanding the STATUS Register for the definition and behavior of the STATUS Register.

### 2.4.7 Authentication Status Register

The ATAES132A Authentication Status Register stores the result of most recent authentication attempt. The Authentication Status Register contains the Authentication KeyID, the AuthComplete status flag, and the authentication usage restriction bits. Prior to executing the Auth command, the AuthComplete status flag is set to NoAuth. After successful Inbound Only or Mutual Authentication, the AuthComplete status flag is set to YesAuth.

# ATAES132A

Memory

| Name            | Description                                                                                                                                                    | Write                       | Read   | Bytes |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------|-------|

| Algorithm       | Algorithm ID code (0x0000).                                                                                                                                    | Never                       | Always | 2     |

| ChipConfig      | Device-level cryptographic and power-up configuration options.                                                                                                 | If LockConfig =<br>Unlocked | Always | 1     |

| Counters        | 16 high-endurance counters, each capable of counting<br>to 2M.If LockConfig =<br>UnlockedSee Appendix H. Understanding Counters.Unlocked                       |                             |        |       |

| CounterConfig   | Configuration information for each counter.<br>See Section Counter Configuration.                                                                              | If LockConfig =<br>Unlocked | Always | 32    |

| DeviceNum       | Microchip device number code.                                                                                                                                  | Never                       | Always | 1     |

| EEPageSize      | Length in bytes of physical EEPROM page (32, 0x20).                                                                                                            | Never                       | Always | 1     |

| EncReadSize     | Maximum data length in bytes for EncRead (32, 0x20).                                                                                                           | Never                       | Always | 1     |

| EncWriteSize    | Maximum data length in bytes for EncWrite (32, 0x20).                                                                                                          | Never                       | Always | 1     |

| FreeSpace       | Free memory for customer data storage.                                                                                                                         | If LockConfig =<br>Unlocked | Always | 96    |

| JEDEC           | Microchip JEDEC manufacturer code (0x001F).                                                                                                                    | Never                       | Always | 2     |

| KeyConfig       | Configuration information for each key. See Section Key Configuration.                                                                                         | If LockConfig =<br>Unlocked | Always | 64    |

| LockConfig      | Controls Configuration Memory Write access, except SmallZone. Default is the Unlocked state. (Note 2)                                                          | Via Lock Command<br>Only    | Always | 1     |

| LockKeys        | Controls Key Memory Write access.<br>Default is the Unlocked state. (Note 2)                                                                                   | Via Lock Command<br>Only    | Always | 1     |

| LockSmall       | Controls SmallZone Register Write access.<br>Default is the Unlocked state. (Note 2)                                                                           | Via Lock Command<br>Only    | Always | 1     |

| LotHistory      | Microchip proprietary manufacturing information.                                                                                                               | Never                       | Always | 8     |

| ManufacturingID | Two byte manufacturing ID code.                                                                                                                                | Never                       | Always | 2     |

| PermConfig      | Microchip factory device configuration options.                                                                                                                | Never                       | Always | 1     |

| SerialNum       | erialNum Guaranteed unique die serial number. SerialNum is optionally included in cryptographic calculations. See Appendix E. SerialNum Register.              |                             | Always | 8     |

| SmallZone       | allZone 32 byte value. The first four bytes are optionally If LockSmall = Unlocket included in cryptographic calculations. See Appendix E. SmallZone Register. |                             | Always | 32    |

| I2CAddr         | Selects the serial interface mode and stores the $I^2C$ Device Address.                                                                                        | If LockConfig =<br>Unlocked | Always | 1     |

| ZoneConfig      | Access and usage permissions for each user zone.<br>See Section User Zone Configuration.                                                                       | If LockConfig =<br>Unlocked | Always | 64    |

| Table 2-1 | . Summary | of the | Configuration | Memory | Registers | Sorted b | y Register | ' Name <sup>(Note 1)</sup> |

|-----------|-----------|--------|---------------|--------|-----------|----------|------------|----------------------------|

|-----------|-----------|--------|---------------|--------|-----------|----------|------------|----------------------------|

### Note:

- 1. Changes to most of the configuration registers take effect immediately which allows the functionality to be tested during the personalization process. Changes to the I2CAddr register take effect at the next Reset, Power Up, or Wake-Up from the Sleep state.

- 2. The LockConfig, LockKeys, and LockSmall bytes can only be changed with the Lock command (see Section User Zone ReadOnly Activation). **Warning**: ATAES132A must always be locked by the customer prior to shipment to the end user to protect the customer secrets.

# 3. Security Features

All ATAES132A security features are optional. Each feature is enabled or disabled by programming configuration bits in the EEPROM Configuration Memory. Each user zone, Key, and Counter is separately and independently configured.

This section describes the ATAES132A security features and cryptographic capabilities. The functionality associated with each portion of the memory is described in Section Memory.

# 3.1 Architecture

ATAES132A contains all circuitry for performing authentication, encryption, and decryption using keys stored securely in the internal EEPROM. Since the secrets are stored securely in the ATAES132A, they do not have to be exchanged prior to executing cryptographic operations.

ATAES132A has fixed cryptographic functionality; it is not a microcontroller and cannot accept customer firmware. ATAES132A contains a hardware AES cryptographic engine and has a fixed command set. Although the functionality is fixed, it is also flexible because each feature is enabled or disabled by the customer by programming registers in the EEPROM Configuration Memory. After personalization is complete, fuses lock the configuration so it cannot be changed.

### 3.1.1 AES

The ATAES132A cryptographic functions are implemented with a hardware cryptographic engine using AES in CCM mode with a 128-bit key. AES-CCM mode provides both confidentiality and integrity checking with a single key. The integrity MAC includes both the encrypted data and additional authenticate-only data bytes, as described in each command definition. Each MAC is unique due to inclusion of a Nonce and an incrementing MacCount Register in the MAC calculation.

See Appendix I. Cryptographic Computations for information about how the AES computations are performed. Hyperlinks to the AES standard are provided in Appendix A. Standards and Reference Documents.

### 3.1.2 Hardware Security Features

The ATAES132A device contains physical security features to prevent an attacker from determining the internal secrets. ATAES132A includes tamper detectors for voltage, temperature, frequency, and light, as well as an active metal shield over the circuitry, internal memory encryption, and other various features. The ATAES132A physical design and cryptographic protocol are designed to prevent or significantly complicate most algorithmic, timing, and side-channel attacks.

### 3.2 Authentication

The authentication commands utilize AES-CCM to generate or validate a MAC value computed using an internally stored key. The command set supports both one-way and mutual authentication. One ATAES132A device can generate packets for authentication of a second ATAES132A device containing the same key. The internal authentication status register remembers only the most recent authentication attempt. A user zone can be configured to require prior authentication of a designated key before access to the user zone is permitted.

### 3.2.1 Key Authentication

Individual keys can be configured to require a successful authentication prior to use. This requirement can be used to prevent some kinds of exhaustive attacks on the keys. The authentication requirement

can be chained to require authentication of several keys prior to allowing a particular operation. The internal Authentication Status Registers remembers only the most recent authentication attempt.

# 3.3 Encrypted Memory Read/Write

A user zone can be configured to require AES-CCM encryption for EEPROM Read or Write operations. If encryption is required for Write access, then the MAC is validated before the received (encrypted) data are written to the EEPROM. If encryption is required for read access, then ATAES132A encrypts data when they are read from the internal EEPROM, and generates an associated integrity MAC.

# 3.4 Data Encryption/Decryption

A key can be configured to allow encryption or decryption of small packets of data using AES-CCM with an internally stored key. The Encrypt command encrypts 16 or 32 bytes of plaintext data provided by the Host; the encrypted data, and MAC are returned to the Host. The Decrypt command decrypts 16 or 32 bytes of encrypted data after verifying the MAC; the data is returned to the Host only if the MAC is valid. When these commands are used, none of the data is stored in the internal EEPROM.

### 3.4.1 AES-ECB Encryption/Decryption

A key can be configured to allow AES-ECB mode operations using the Legacy command. A single AES-ECB operation is performed using an internally stored key and the 16-byte input packet received with the AES-ECB command. The 16-byte result is returned to the Host. No input or output formatting is performed by this command, and no data is stored in the internal EEPROM.

# 3.5 Keys

The ATAES132A securely stores sixteen 128-bit keys in the EEPROM. Keys can only be used for the cryptographic functions enabled in the ZoneConfig, CounterConfig, or KeyConfig Register bits in the Configuration Memory. Key values can never be read from ATAES132A under any circumstances. Any key can be used with any user zone.

A seventeenth key register in the internal SRAM can be used for session keys.

See Section Encrypted Key Writes, for the EncWrite command. See Section User Zone ReadOnly Activation, for the Lock command.

### 3.5.1 Key Management

The Key registers can be written with plaintext data or with encrypted data before the Key Memory is locked. After the Key Memory is locked, a key register can only be updated only if the corresponding KeyConfig Register allows updates.

Several key management commands are available for updating or generating the keys:

- 1. An encrypted key provided by the Host can be written to an internal key register after validating the MAC. The KeyImport command and KeyLoad command performs this function.

- 2. The internal RNG can be used to create a key for use as a session key or for storage in an internal Key Register. The new key can be encrypted and returned to the Host for use as the encrypted key input to another ATAES132A device. The KeyCreate command performs this function.

- Keys stored in User Memory can be transferred to an internal key register or used as a session key. A user zone configured as extended Key Memory can be used to store eight keys. The KeyTransfer command performs this function.

### 3.5.2 Limited Use Keys

To prevent exhaustive attacks on the keys, the ATAES132A can be configured to limit key usage with a Counter. If a key is configured with a Usage Counter, then the following steps are performed for any command using that key:

- 1. Read the Counter from memory to check if the count has reached the maximum count value.

- 2. If the maximum count has been reached, then the command is not executed and an error code is returned.

- 3. If the maximum count has not been reached, then the Counter is incremented and the command is executed.

By default, the Counters are configured to allow the maximum value of 2,097,051 counts, allowing 2,097,051 operations using a key with the usage limits enabled. Microchip recommends the customer configure the Key Usage Counters to a smaller number at personalization; the appropriate key usage limit is dependent on the application. See Appendix H. Understanding Counters for additional information.

#### 3.5.2.1 Key Diversification

Microchip recommends that each unit should contain one or more unique keys to minimize the potential impact of cloning. The keys stored in the ATAES132A should be a cryptographic combination of a root secret not stored in the device along with the unique ATAES132A SerialNum Register value. The Host must have a secure place to store the root secret to protect the integrity of the diversified keys.

It may also be beneficial for the ATAES132A devices to contain secrets for validating the authenticity of the Host. These secrets may need to be the same on all ATAES132A devices for a particular application to permit any Client to validate any Host. See Section KeyCreate Command, Mode<2>.

### 3.6 Random Numbers

The ATAES132A includes a high-quality RNG for Nonce generation, child key creation, and general random number generation. The ATAES132A commands can generate random numbers for internal or external use. Sixteen byte random numbers for external use are generated using the internal RNG and the AES engine, as described in NIST SP800-90.

The RNG can be used to generate the Nonce for cryptographic operations. A mechanism is also provided to synchronize the Nonces in two ATAES132A devices using random numbers generated by both devices. A key can be configured to require that the cryptographic operations using the key use a Nonce generated with the internal RNG.

### 3.6.1 Random Number Generation

The RNG architecture includes both a hardware RNG and a stored random seed. On power-up, the stored seed is read from the EEPROM, cryptographically combined with the hardware RNG output, and then stored in SRAM. Whenever a random number is required, this SRAM Seed is cryptographically combined with the hardware RNG output and the optional input seed to create both a new SRAM Seed and the random number.

For the highest security, the EEPROM Seed should be updated at every power cycle in which the RNG is used. However, the EEPROM Seed Register has a maximum life expectancy of 100,000 writes per unit. The Host system is expected to manage the EEPROM Seed by using the command mode option to suppress automatic EEPROM Seed updates.

# 4. Security Configuration Registers

# 4.1 User Zone Configuration

Access permissions to each user zone are controlled by the ZoneConfig Registers in the Configuration Memory. There is one ZoneConfig Register for each User Memory zone.

| ZoneConfig Field   | Byte | Bit | Description                                                                                                                                                                                                                                                               |  |

|--------------------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| UseSmall           | 0    | 7   | <ul> <li>0b = First four bytes of SmallZone are not included in the EncWrite Operations.</li> <li>1b = First four bytes of SmallZone must be included in the EncWrite operation provided the EncWrite = 1b. If EncWrite = 0b then the UseSmall bit is ignored.</li> </ul> |  |

| UseSerial          | 0    | 6   | <ul> <li>0b = SerialNum is not included in the EncWrite operations.</li> <li>1b = SerialNum is included in the EncWrite operations provided EncWrite = 1b. If EncWrite = 0b then the UseSerial bit is ignored.</li> </ul>                                                 |  |

| WriteMode          | 0    | 5:4 | 00b = Zone is permanently read/write.<br>01b = Zone is permanently read-only.                                                                                                                                                                                             |  |

|                    |      |     | 10b = The ReadOnly byte determines if writes are permitted.                                                                                                                                                                                                               |  |

|                    |      |     | 11b = The ReadOnly byte determines if writes are permitted, and the Lock command must include an authenticating MAC calculated using the KeyID stored in ZoneConfig[UZ].WriteID .                                                                                         |  |

| EncWrite           | 0    | 3   | 0b = Encryption is not required to write data.<br>1b = Encryption is required to write data.                                                                                                                                                                              |  |

| EncRead            | 0    | 2   | 0b = Encryption is not required to read data.<br>1b = Encryption is required to read data.                                                                                                                                                                                |  |

| AuthWrite          | 0    | 1   | <ul><li>0b = Authentication is not required to write data.</li><li>1b = Authentication is required to write data.</li></ul>                                                                                                                                               |  |

| AuthRead           | 0    | 0   | 0b = Authentication is not required to read data.<br>1b = Authentication is required to read data.                                                                                                                                                                        |  |

| AuthID             | 1    | 7:4 | KeyID which is used for inbound authentication before access is permitted.                                                                                                                                                                                                |  |

| ReadID             | 1    | 3:0 | KeyID which is used to encrypt data read from this zone. The same key is used to generate the MAC.                                                                                                                                                                        |  |

| WriteID            | 2    | 7:4 | KeyID that is used to decrypt data written to this zone. The same key is used to verify the MAC.                                                                                                                                                                          |  |

| Reserved           | 2    | 3:1 | Reserved for future use.                                                                                                                                                                                                                                                  |  |

| VolatileTransferOK | 2    | 0   | 0b = Key transfer from this User Zone to VolatileKey is prohibited.<br>1b = Key transfer from this User Zone to VolatileKey is permitted.                                                                                                                                 |  |

| ReadOnly           | 3    | 7:0 | The contents of this byte are ignored unless WriteMode contains $10b$ or $11b$ .<br>If $0x55$ , then the user zone is Read/Write.                                                                                                                                         |  |

|                    |      |     | If any other value, then the user zone is read-only.                                                                                                                                                                                                                      |  |

Table 4-1. Definition of the ZoneConfig Register Bits <sup>(1)</sup>

| ZoneConfig Field | Byte | Bit | Description                                                                                                              |

|------------------|------|-----|--------------------------------------------------------------------------------------------------------------------------|

|                  |      |     | This byte can be updated after the Configuration Memory is locked using the $Lock$ command (See Section $Lock$ Command). |

Note:

Most changes to the ZoneConfig Registers take effect immediately. Changes to the AuthRead and EncRead bits do not affect the SPI or I<sup>2</sup>C Read command until the next reset or power-up.

Warning: The ATAES132A must always be locked by the customer prior to shipment to the end user to protect the customer secrets. See Section Lock Command.

# 4.2 Key Configuration

Restrictions on key usage are controlled by the KeyConfig Registers in the Configuration Memory. There is one KeyConfig Register for each key.

| KeyConfig Field | Byte | Bit | Description                                                                                                                                                                                                                                                                                                                              |

|-----------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ChangeKeys      | 0    | 7   | Ob = Key updates with EncWrite command are prohibited.<br>1b = Key updates are permitted after locking. The new key is written using the<br>EncWrite command with a MAC generated with the current value of key.<br>See Section EncWrite Command.                                                                                        |

| Parent          | 0    | 6   | 0b = This use is prohibited.<br>1b = This key can be used as the parent when writing VolatileKey via KeyCreate,<br>KeyImport, or KeyLoad. See Section VolatileKey Configuration.                                                                                                                                                         |

| Child           | 0    | 5   | 0b = This use is prohibited.<br>1b = The key is permitted to be the target of a KeyCreate or KeyLoad command.                                                                                                                                                                                                                            |

| AuthKey         | 0    | 4   | 0b = Prior authentication is not required.<br>1b = The key requires prior authentication using the KeyID stored in LinkPointer.                                                                                                                                                                                                          |

| LegacyOK        | 0    | 3   | 0b = The key cannot be used with the Legacy command.<br>1b = The key can be used with the Legacy command.                                                                                                                                                                                                                                |

| RandomNonce     | 0    | 2   | 0b = The Nonce is not required to be random.<br>1b = Operations using this key requires a random Nonce. See Section Nonce<br>Command.                                                                                                                                                                                                    |

| InboundAuth     | 0    | 1   | 0b = The key can be used for any purpose not prohibited by another KeyConfig bit,<br>including Outbound Only authentication.<br>1b = The key can only be used by the Auth command for Inbound Only or Mutual<br>Authentication. The key cannot be used by any other command, but KeyID can be<br>the target of a key management command. |

| ExternalCrypto  | 0    | 0   | <pre>0b = The Encrypt and Decrypt commands are prohibited. 1b = The key can be used with the Encrypt and Decrypt commands.<sup>(3)</sup></pre>                                                                                                                                                                                           |

| AuthCompute     | 1    | 7   | 0b = The key cannot be used with the AuthCompute command.<br>1b = The key can be used with the AuthCompute command.                                                                                                                                                                                                                      |

| Table 4-2. Definition of the KeyConfig Register Bi | s (Notes 1, 2, 4 | ) |

|----------------------------------------------------|------------------|---|

|----------------------------------------------------|------------------|---|

1

6

TransferOK

0b = KeyTransfer command is prohibited.

# ATAES132A Security Configuration Registers

| KeyConfig Field | Byte | Bit | Description                                                                                                                                                                                                                                                                                                                                          |  |

|-----------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 |      |     | 1b = The key is permitted to be the target of a KeyTransfer command. See Section KeyTransfer Command.                                                                                                                                                                                                                                                |  |

| ChildAuth       | 1    | 5   | 0b = Prior authentication is not required.<br>1b = The KeyCreate command requires prior authentication using the KeyID stored<br>in LinkPointer.                                                                                                                                                                                                     |  |

| ImportOK        | 1    | 4   | <pre>0b = KeyImport command is prohibited. 1b = The key is permitted to be the target of a KeyImport command.</pre>                                                                                                                                                                                                                                  |  |

| AuthOutHold     | 1    | 3   | $\begin{array}{l} 0 \mbox{$^{\rm b}$ = Then the I}^2 C \mbox{ AuthO output is reset when an authentication reset is executed} \\ using this key (see Appendix J. I}^2 C \mbox{ Auth Signaling}). \\ 1 \mbox{$^{\rm b}$ = The I}^2 C \mbox{ AuthO output state is unchanged when an authentication reset is} \\ executed using this key. \end{array}$ |  |

| AuthOut         | 1    | 2   | $0b = I^2C$ Auth signaling is disabled for this key.<br>$1b = I^2C$ Auth signaling is enabled for this key (see Appendix J. $I^2C$ Auth Signaling).                                                                                                                                                                                                  |  |

| ChildMac        | 1    | 1   | <pre>0b = The KeyCreate command does not require an input MAC (it will be ignored<br/>provided).<br/>1b = An input MAC is required to modify this key using the KeyCreate command</pre>                                                                                                                                                              |  |

| CounterLimit    | 1    | 0   | 0b = No usage limits.<br>1b = Usage count limits are enabled for this key (see CounterNum).                                                                                                                                                                                                                                                          |  |

| CounterNum      | 2    | 7:4 | Stores the CntID of the Monotonic Counter attached to this key for usage limits or for MAC calculation. MAC calculations will include the Counter if Command Mode<5> is 1b even if key usage limits are disabled.                                                                                                                                    |  |

| LinkPointer     | 2    | 3:0 | For child keys; stores the ParentKeyID.<br>For all other keys; the KeyID of the authorizing key (see AuthKey).                                                                                                                                                                                                                                       |  |

| Reserved        | 3    | 7:1 | Reserved for future use.                                                                                                                                                                                                                                                                                                                             |  |

| DecRead         | 3    | 0   | <pre>0b = The DecRead and WriteCompute are prohibited. 1b = The DecRead and WriteCompute commands can be run using this key.</pre>                                                                                                                                                                                                                   |  |

### Note:

- 1. Changes to the KeyConfig Registers take effect immediately which allows the functionality to be verified during the personalization process.

- 2. **Warning**: The ATAES132A must always be locked by the customer prior to shipment to the end user to protect the customer secrets. See Section Lock Command.

- 3. **Warning**: Since the Encrypt command does not include an input MAC, the Encrypt command can exhaustively be run with selected input data to attack the key. Requiring authentication prior to allowing encryption makes these attacks more difficult. To require prior authentication, the AuthKey and RandomNonce bits must be set to 1b.

- 4. A key can be disabled by setting KeyConfig[KeyN].AuthKey to 1b, and KeyConfig[KeyN].LinkPointer to contain "KeyN", where KeyN = KeyID of the key being configured.

# 4.3 VolatileKey Configuration

There is a seventeenth key register, named VolatileKey, which has a KeylD of 0xFF and is stored in the internal SRAM. This key location can be written with the KeyCreate (see Section KeyCreate Command), KeyImport (see Section KeyImport Command), KeyLoad (see Section KeyLoad Command), or KeyTransfer (see Section KeyTransfer Command) commands. The contents of the VolatileKey Register are erased when the device is powered down, enters the Sleep state, or is reset.

When the VolatileKey Register is loaded, restrictions are placed on its usage which persists until the power is lost or the key is reloaded. The definition of the VolUsage field is shown in the table below.

| VolUsage Field<br>Name | Byte | Bit | Description                                                                                                                                                                                                                             |

|------------------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved               | 0    | 7   | Reserved for future use. All bits must be 0b.                                                                                                                                                                                           |

| LegacyOK               | 0    | 6   | 0b = Legacy command is prohibited.<br>1b = Legacy command can be run using this key.                                                                                                                                                    |

| AuthCompute            | 0    | 5   | 0b = AuthCompute command is prohibited.<br>1b = AuthCompute command can be run using this key.                                                                                                                                          |

| RandomNonce            | 0    | 4   | 0b = A fixed (input-only) Nonce is permitted.<br>1b = Operations using this key require a random Nonce (see Section Nonce<br>Command).                                                                                                  |

| DecryptOK              | 0    | 3   | 0b = Decrypt command is prohibited.<br>1b = Decrypt command can be run using this key.                                                                                                                                                  |

| EncryptOK              | 0    | 2:1 | 00b = Encrypt command is prohibited.<br>01b = Encrypt command can be run using this key without a prior<br>authentication. Note 1<br>10b or 11b = Encrypt command can be run using this key only with a prior<br>authentication. Note 1 |

| AuthOK                 | 0    | 0   | 0b = Auth command is prohibited.<br>1b = Auth command can be run using this key.                                                                                                                                                        |

| Reserved               | 1    | 7:2 | Reserved for future use. All bits must be 0b.                                                                                                                                                                                           |

| DecRead                | 1    | 1   | 0b = DecRead command is prohibited.<br>1b = DecRead command can be run using this key.                                                                                                                                                  |

| WriteCompute           | 1    | 0   | <pre>0b = WriteCompute command is prohibited. 1b = WriteCompute command can be run using this key.</pre>                                                                                                                                |

| Table 4-3. VolUsage Field Bit Definitions in the KeyCreate or KeyLoad Command at VolatileKey |

|----------------------------------------------------------------------------------------------|

| Creation                                                                                     |

#### Note:

1. **Warning**: Since the Encrypt command does not include an input MAC, the Encrypt command can be exhaustively run with selected input data to attack VolatileKey. Requiring authentication prior to allowing encryption makes these attacks more difficult. To implement this, the Auth and RandomNonce bits must be set to 1b, and the Encrypt bits must be set to 10b or 11b when the VolatileKey is created.

# 4.4 Counter Configuration

The CounterConfig Registers impose restrictions on the usage of the Counter command with a Counter (see Section Counter Command). There is one CounterConfig Register for each Counter. Each Counter can increment up to a value of 2,097,151 using the Count command, after which they can no longer be changed. See Appendix H. Understanding Counters for additional Counter information.

The CounterConfig bits have no impact on the functionality of a Key Usage Counter. If a Counter is identified in a KeyConfig Register (see Section Key Configuration) as a Key Usage Counter, then the Counter will increment each time the key is used. The CounterConfig[CntID].IncrementOK bit is typically set to 0b to prohibit the Counter command from incrementing a Key Usage Counter.

| CounterConfig Field | Byte | Bit | Description                                                                                                           |

|---------------------|------|-----|-----------------------------------------------------------------------------------------------------------------------|

| Reserved            | 0    | 7:2 | Reserved for future use. All bits must be 0b.                                                                         |

| RequireMAC          | 0    | 1   | 0b = An input MAC is prohibited.<br>1b = The increment operation requires an input MAC.                               |

| IncrementOK         | 0    | 0   | 0b = Increments using the Counter command are prohibited.<br>1b = Increments using the Counter command are permitted. |

| MacID               | 1    | 7:4 | KeyID of the key used to generate the Counter command output MAC for Counter Read operations.                         |

| IncrID              | 1    | 3:0 | KeyID of the key used to generate the Counter command input MAC for increment operations.                             |

Table 4-4. CounterConfig Register Bit Definitions (Notes 1, 2)

### Note:

- 1. Changes to the CounterConfig Registers take effect immediately, allowing the functionality to be verified during the personalization process.

- 2. Warning: The ATAES132A must always be locked by the customer prior to shipment to the end user to protect the customer secrets. See Section Lock Command.

# 5. Standard Serial EEPROM Read and Write Commands

This section provides a summary of the operations that can be performed using the standard Serial EEPROM Read and Write commands. For detailed information, see the specification sections that are referenced below.

Table 5-1. Standard Serial EEPROM Read and Write Commands

| Name  | Description                                                                                                                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read  | The Read command is used to read cleartext from the user zones, to retrieve a response by reading the Response Memory Buffer, or to read the STATUS Register.                                                               |

| Write | The Write command is used to write cleartext to unrestricted memory or to send a command by writing the command packet to the Command Memory Buffer. The Write command is also used to write the IO Address Reset Register. |

# 5.1 Read

The ATAES132A supports the standard Serial EEPROM commands to read from the User Memory. All bytes in the User Memory address space may be read; however, only bytes in the user zones in which neither authentication nor encryption is required will return the actual data from the memory. All other locations will return the value  $0 \times FF$ . See Appendix J. I<sup>2</sup>C Interface for I<sup>2</sup>C Read command information and Appendix K. SPI Interface for SPI Read command information.

When a Read command is received, the device looks at the AuthRead and EncRead bits in the ZoneConfig Register for the user zone to determine whether to return  $0 \times FF$  or the EEPROM data. If the EncRead bit is 1b or the AuthRead bit is 1b, then  $0 \times FF$  will always be returned.

If the ZoneConfig AuthRead bit is 1b and the EncRead is 0b, then the BlockRead command must be used to read the user zone (see Section BlockRead Command). If the EncRead bit is 1b, then the EncRead command must be used to read the user zone (see Section EncRead Command).

The standard SPI and I<sup>2</sup>C Read commands can be used to read any number of bytes in a single operation. Read operations can cross EEPROM page boundaries.

### 5.1.1 Read the Response Memory Buffer

The Host sends the ATAES132A commands to the device by writing the command packet to the Command Memory Buffer using a standard SPI or I<sup>2</sup>C Write command. ATAES132A processes the command packet and places the response in the Response Memory Buffer. The Host retrieves the response by reading the response packet using a standard SPI or I<sup>2</sup>C Read command. See Appendix D. Command Memory Map for additional information. See Appendix G. Understanding the STATUS Register for examples.

When any error occurs, the EERR bit of the STATUS Register is set to 1b to indicate an error. See Appendix G. Device Status Register (STATUS) Definition for more information.

### 5.1.2 Read the Key Memory or Configuration Memory

Reading the Key Memory is never allowed.

The Read command can never be used to read data from the Configuration Memory. The BlockRead command is used to access the Configuration Memory (see Section BlockRead Command).

If a standard SPI or I<sup>2</sup>C Read command is used within the Configuration Memory or Key Memory address space, then  $0 \times FF$  will be returned for each byte.  $0 \times FF$  is also returned for address locations that do not physically exist. The EERR bit of the STATUS Register is set to 1b if  $0 \times FF$  was substituted for any byte returned by a read command. See Appendix G. Device Status Register (STATUS) Definition for more information.

### 5.1.3 Read the STATUS Register

The Host reads the STATUS Register by reading address 0xFFF0. In SPI interface mode, the Host can also read STATUS using the RDSR command. See Appendix G, Understanding the STATUS Register, for detailed information and examples.

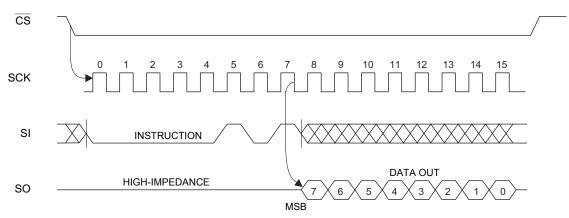

### 5.2 Write